AEi Systems

5933 W. Century Blvd. Ste 1100

Los Angeles, CA 90045

+1-702-625-0568

aeisystems.com

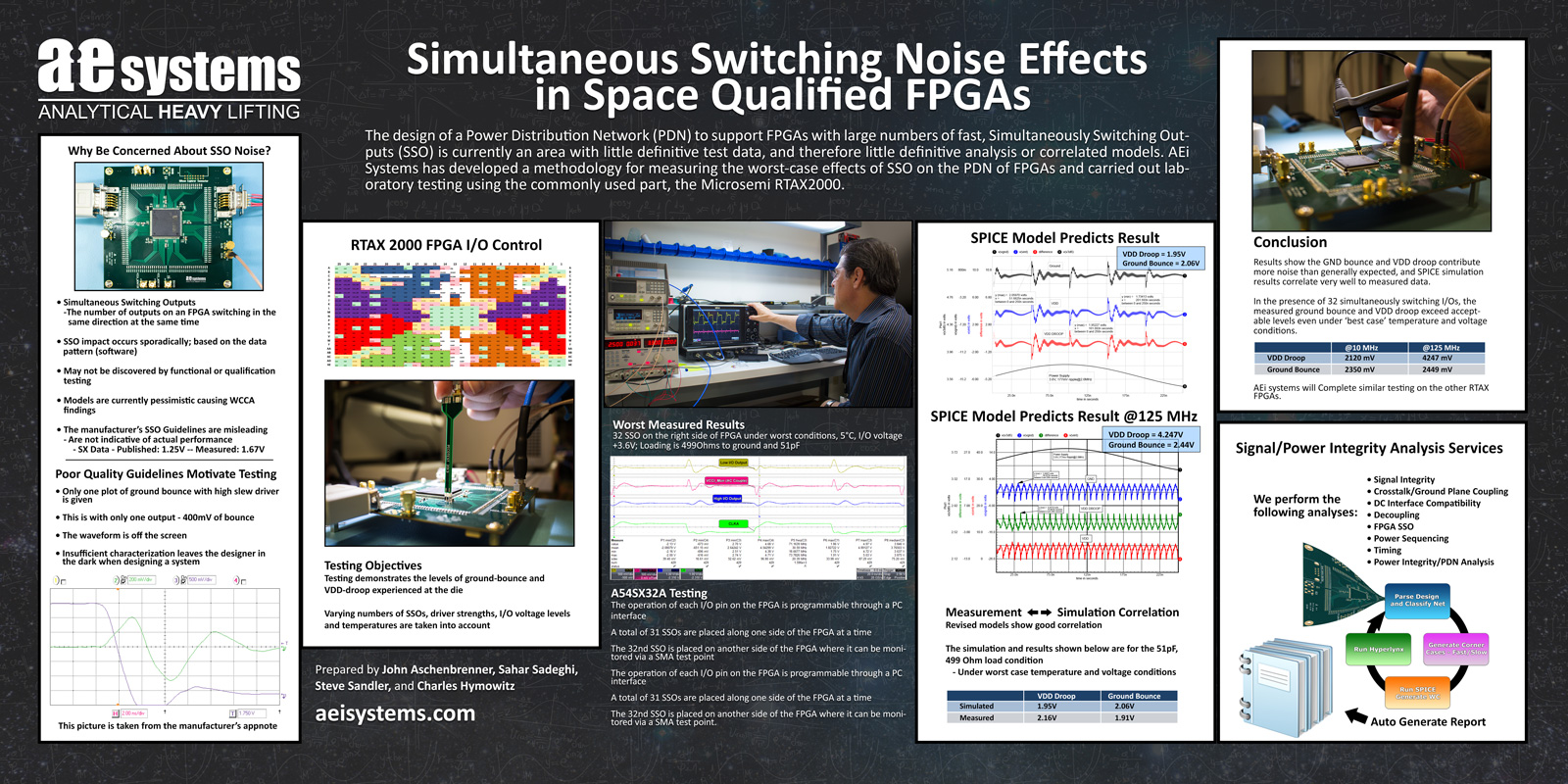

This month’s articles cover two hot topics: SSO Noise For Space Qualified (RTAX) FPGAs and SPICE Modeling

SSO Noise Effects in RTAX FPGAs

For some time, SSO performance has been a source of concern for designers due to

poor packaging performance and limited performance data for the space grade devices.

Good design practices and guidelines are needed, but without detailed data and models,

designs are having real issues.

AEi Systems has developed a methodology for measuring the effects of SSO on the

PDN performance of FPGAs and carried out laboratory testing using one of the most

commonly used parts, the Microsemi RTAX2000.

The point of it all - AEi Systems is using the data to create accurate high-fidelity

SPICE models correlated to SSO Noise performance that can be used to perform nominal,

best, and worst case SSO analysis on our customer’s particular designs. The models

can be customized to each FPGA configuration (strength, quantity and proximity of

I/Os, board and decoupling capacitance).

AEi Systems has completed testing of the Simultaneous Switching Noise (SSO/SSN)

performance of the Microsemi SX32 device, a prelude to testing the RTAX2000. A report

on the SX results can be found here, http://www.aeng.com/power_integrity.htm under

“SSO Noise Effects in RTAX FPGAs - Part 1.”

Lessons Learned from SPICE

(Downloadable Presentation)

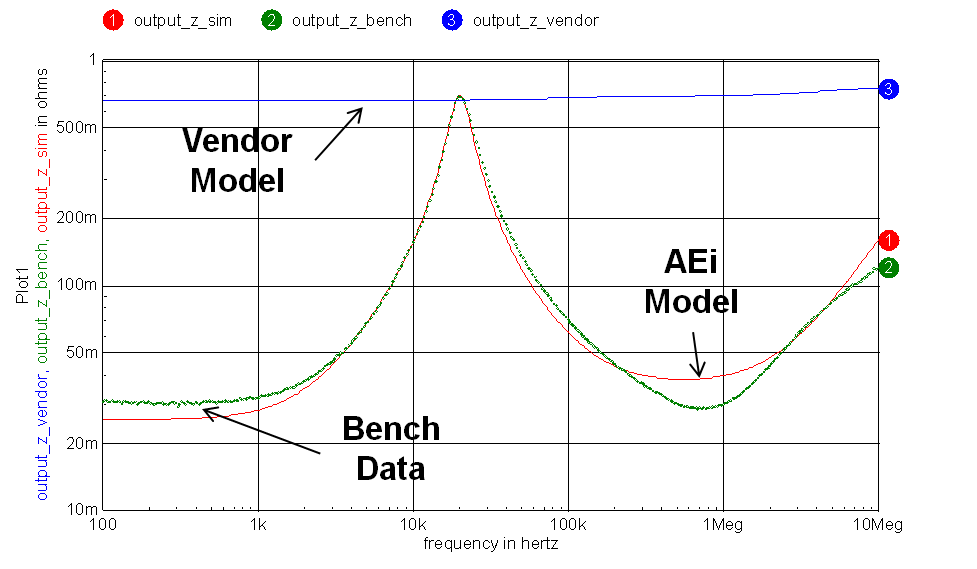

This presentation highlights many of the pitfalls and issues surrounding IC vendor

and EDA software vendor supplied SPICE models, as well as SPICE modeling in general.

Several examples of poor IC manufacturer models are discussed including those for

Power Mosfets, Voltage References, and Linear Regulators.

The presentation, originally given at the Aerospace Corp.’s Space Power Workshop

Presentation on May 8, 2014 has been enhanced with additional notes and explanations.

There are many SPICE models available online. Unfortunately, availability doesn’t

necessarily equal usability. The majority of these models have no documentation

or detailed description of the model’s capabilities. More importantly, the limitations

are not discussed, at least not in detail. Rarely is there data correlating the

model performance to test data. This all leaves one to wonder what the model is

and isn’t good for and over what operating conditions is the model valid.

There is so much at stake and yet, despite the lack of model correlation, these

models are often presumed to be correct and used without validation because they

are provided ‘by the vendor.’ Some simple simulations, as shown in this presentation,

reveal this to be a dangerous assumption.

Results To Be Published

The RTAX2000-CGA624 device testing will be complete in just a few short weeks. RTAX2000

test data will include:

- SSO noise (Vdd Droop/Ground Bounce) with 1 – 40 I/Os in a bank, for various driver types (LVTTL 8-24 High, PCI)

- SSO noise on quiet outputs when surrounded by SSO (at various distances)

- Measurements of input disruptions due to SSO when driven by an external driver at various voltages. (0V to 3.6V)

- Measurements of input disruptions (glitches) when driven by another FPGA bank where SSO is present

- Determine if the input value upset (glitch) due to SSO is mitigated by internal or external pull-ups/downs

- Die capacitance (biased/unbiased)

- Input clamp current during SSO event

- PDN/Power Integrity Performance

Please let us know if you, or others you know, are interested in:

Background and Motivations

The results of the FPGA testing show the severity of SSN effects and demonstrate

the accuracy of AEi System’s SSO modeling techniques. Our lab measurements show

SX32 SSN in excess of the amounts advertised in the manufacturer’s application notes.

With thirty-two simultaneously switching I/O the noise produced is all but guaranteed

to disrupt static output logic levels, even under best case temperature and voltage

conditions. Under worst case conditions ground bounce and VDD droop exceed 2 volts,

wreaking havoc on digital interfaces.

The collection of test data is necessary to refine models which are used to predict

the performance of various design configurations. Improved modeling allows designers

to avoid potential issues by identifying them early, when they can be mitigated.

The results of our RTAX2000 measurements will be used to improve the fidelity of

our SSO modeling done in SPICE. This modeling will allow us to analyze the SSO performance

of any customer-specific design.

In order to test the RTAX2000 we’ve designed a sophisticated test platform allowing

accurate measurement of SSN and its effects, under many operating scenarios, all

controlled by our custom test software. Our flight-like, 16 layer test board features

fifty RF connector test points allowing us to measure not just SSN, but also part

package parasitics and power plane impedance. We are able to perform similar testing

for any programmable device of interest to you and your projects.

As presented at MAPLD 2014

Cheaper than in-house resources

- Our full-time team of top engineers with focused backgrounds in reliability, design, WCCA, and test has all the required core competencies to perform with great efficiency.

- We have a significant number of SPICE models already made. We have Parts Variability Databases. We have Radiation Data. Even if you have in-house resources, dealing with models and tolerances can take a significant amount of time. AEi Systems puts the money and time savings in your pocket as we do not charge extra for this valuable IP

- Analysis is all we do; Keep your in-house designers doing what they do best.

Faster than in-house resources - ready to go

- Our proprietary software tools, library of proven SPICE models, and our 20 years of analytical engineering experience keep your team ahead of schedule

- No bias - We introduce "checks and balances" to your design process/SDRLs

How can we help you? Contact us for more specific information or a no-obligation quotation.